# ZIQIAO ZHOU<sup>\*</sup>, Microsoft Research, USA MICHAEL K. REITER<sup>\*</sup>, Duke University, USA

Noninterference measurement quantifies the secret information that might leak to an adversary from what the adversary can observe and influence about the computation. Static and high-fidelity noninterference measurement has been difficult to scale to complex computations, however. This paper scales a recent framework for noninterference measurement to the open-source RISC-V BOOM core as specified in Verilog, through three key innovations: logically characterizing the core's execution incrementally, applying specific optimizations between each cycle; permitting information to be declassified, to focus leakage measurement to only secret information that cannot be inferred from the declassified information; and interpreting leakage measurements for the analyst in terms of simple rules that characterize when leakage occurs. Case studies on cache-based side channels generally, and on specific instances including SPECTRE attacks, show that the resulting toolchain, called DINOME, effectively scales to this modern processor design.

#### ACM Reference Format:

## **1 INTRODUCTION**

Noninterference [Goguen and Meseguer, 1982] is a classic information flow policy that, informally, requires that an attacker's view be unaffected by the values that should remain secret to it. Since systems often necessarily leak some information, however, a more practical goal is to insist that the interference be "small", which in turn requires that it be measured in some way. Various methodologies have been proposed for doing so statically (e.g., Backes et al. [2009], Phan and Malacaria [2014], Zhang et al. [2010]), though these techniques invariably must balance a tension between measurement fidelity and scalability to complex computations.

A recent advance in this domain was due to Zhou et al. [2018], which formulated noninterference measurement in terms of a *projected model counting* problem that, in turn, was amenable to relatively efficient, *approximate* model counting methods. Their measurement approach, however, scales to programs of only modest complexity, for two reasons. Computationally, their technique relies on symbolic execution to generate a logical postcondition for the computation for which noninterference is to be measured. For example, this step alone required six hours for Smaz and eight hours for Gzip, using 16 cores, for extracting postconditions to measure the risk of CRIME attacks [Kelsey, 2002] against these compression libraries. More qualitatively, while their technique

<sup>\*</sup>Work performed in part at the University of North Carolina, Chapel Hill, NC, USA.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

OOPSLA '21, Chicago, IL

<sup>© 2022</sup> Association for Computing Machinery.

ACM ISBN 978-x-xxxx-x/YY/MM...\$15.00

https://doi.org/10.1145/nnnnnnnnnnnn

provides a measurement of interference, it provides the analyst little assistance in interpreting the measurement or focusing the analysis on particular aspects of the leakage.

While noninterference measurement for arbitrary computations remains out of reach, in this paper we adapt the approach of Zhou et al. [2018] to address the previous shortcomings within a particularly important and complex domain, namely information leaks arising in hardware processors. Leakage of software secrets due to processor optimizations have attracted massive attention in recent years, especially since the discovery of vulnerabilities arising due to the footprint of speculative executions in processor caches (SPECTRE [Kocher et al., 2019], MELTDOWN [Lipp et al., 2018], and variants). Even though many defenses (e.g., Tan et al. [2020], Wang and Lee [2007], Werner et al. [2019], Zhou et al. [2016]) have been proposed to interfere with cache-based side channels, we are aware of no measurement methodology to compare designs and evaluate their effectiveness, working directly from their Verilog specifications. Adapting a technique like Zhou et al. [2018] to do so, moreover, appears difficult: the sheer complexity of modern processor designs both necessitates greater support to help the analyst understand the factors contributing to the leakage and poses significant scaling challenges to such techniques.

In this paper, we present a methodology that does so, using three key methodological advances:

- Our methodology enables analysts to *declassify* certain information, thereby focusing the measurement on any *other* leakage that might be occurring, i.e., leakage that cannot be inferred from the declassified information. For systems as complex as modern processors, this ability is essential to permit analysts to decompose and analyze leakage in a piecemeal fashion.

- The complexity of processor designs means that once leakage is measured, the exact conditions that cause this leakage might not immediately be evident. Our methodology therefore incorporates a method of *interpreting* the leakage, i.e., providing simple rules that indicate circumstances in which leakage will (or will not) occur. These rules facilitate analyst understanding of the root causes of leakage and can guide analysts to declassify leakage that can be ignored. Each such rule is additionally accompanied by a precision and recall, so that analysts can prioritize the rules they address. These rules are expressed in terms of conditions in which leakage occurs, enabling executions to be generated that demonstrate the leakage if desired but hiding the particulars of the executions from analysts if not.

- Since generating a logical postcondition for a processor's execution of a program en masse is intractable, we devise a method to build the postcondition one cycle at a time. To build single-cycle formulas, we abandon symbolic execution, as we found that applying it to hardware designs induces significant path explosion for even one CPU cycle. Instead, we extract the singlecycle formulas without solving for feasible paths, and then leverage a number of aggressive optimizations when stitching single-cycle formulas together to build the postcondition for the processor's multi-cycle execution. In doing so, we need to be careful that these optimizations preserve the number of assignments to relevant variables across all solutions.

Due to the focus of our methodology on support for declassification and interpretability, we call our tool that realizes it DINOME (for "Declassification and Interpretability for Noninterference Measurement").

To evaluate DINOME, we apply it to evaluate leakage during execution on a RISC-V BOOM core [Celio et al., 2017], a state-of-the-art public domain processor design. Our improvements to generating logical postconditions for execution permit DINOME to do so for more than 100 cycles of this core. This, in turn, permits us to evaluate leakage from cache-based side channels (PRIME+PROBE [Osvik et al., 2006] and FLUSH+RELOAD [Yarom and Falkner, 2014]) in various scenarios, including cryptographic key leakage in sliding-window based modular exponentiation (e.g., Aciiçmez [2007], Percival [2005]), leakage of secrets due to speculative execution, and how this leakage is (incompletely) mitigated by proposed improvements such as SCATTERCACHE [Werner

et al., 2019] and PHANTOMCACHE [Tan et al., 2020]. In each case, we not only measure interference but also generate rules to explain why the leakage occurs, and in some cases refine our view of the leakage using declassification. Our performance evaluation of DINOME indicates that these types of analyses complete in times ranging from seconds to under 15 minutes (using horizontal scaling), after an initial phase to assemble the logical postcondition of up to (only) two hours on (only) a single core.

The rest of this paper is structured as follows. We discuss related work in Sec. 2, and provide both background on the framework on which we build Zhou et al. [2018] and our introduction of declassification to it, our first contribution, in Sec. 3. We present our method for interpreting leakage in Sec. 4. We address implementation challenges in Sec. 5, and then evaluate DINOME through several case studies in Sec. 6. We discuss limitations in Sec. 8 and conclude in Sec. 9.

### 2 RELATED WORK

To our knowledge, DINOME is the first work to measure information leakage from an executable hardware specification instantiated with a software program, in a manner that supports declassification and interpretation of its leakage results.

**Timing side-channel analysis.** Constant-time verification (e.g., Almeida et al. [2016], Barthe et al. [2014], Blazy et al. [2019], Gleissenthall et al. [2019], Zhang et al. [2015]) is a commonly used technique to analyze timing side channels. Software-level verification (e.g., Almeida et al. [2016], Blazy et al. [2019]) checks whether a software program runs in a constant time under specified hardware assumptions. For example, a software-level analysis [Almeida et al., 2016] might conclude that a variable leaks if it is used in a branch condition or as an address in memory access. In a different approach, hardware-level verifiers (e.g., Gleissenthall et al. [2019], Zhang et al. [2015, 2018]) can formally verify the existence of timing side channels using cycle-precise logic derived from hardware specifications. Those works either confirm a constant-time implementation or quantify the timing variation if not, but do not quantify secret leakage due to timing variations in different executions.

**Hardware leakage modeling.** Some works use simplified hardware models instead of real designs (e.g., Chattopadhyay et al. [2017], Doychev et al. [2013], Malacaria et al. [2018]), which makes the computation target feasible but requires more domain knowledge and manual effort to construct the model. Black-box analysis of real systems avoids the use of domain knowledge through a datadriven method that uses sampled data in a real system for estimating the leakage (e.g., Nilizadeh et al. [2019], Oleksii et al. [2020], Song et al. [2001]). In contrast, DINOME measures leakage from hardware specifications written in a hardware design language.

**Quantitative information flow.** QIF (e.g., Gray [1991], Smith [2009, 2011]) represents information leakage through a numeric measurement; most mainstream QIF works (e.g., Chapman and Evans [2011], Phan and Malacaria [2014], Zhang et al. [2010]) use entropy as their measure [Seidenfeld, 1986]. The use of entropy for measuring QIF in actual systems can lead to significant costs, due to the need to compute the input preimage per output value. In addition, real implementations tend to use the most conservative min-entropy measure; e.g., QIF-Verilog [Guo et al., 2019] propagates a min-entropy label per gate and accumulates the leakage across all gates, which overestimates leakage due to its conservative leakage accumulation, especially in large, complex hardware designs (e.g., a CPU core). Entropy also does not distinguish between leaking a few bits in many executions or leaking more bits in a few cases. Alternatives to entropy-based leakage—e.g., differential privacy [Dwork et al., 2006], noninterference measurement [Zhou et al., 2018], classifier-based measurement [Chapman and Evans, 2011], and quantitative hyperproperties [Sahai et al., 2020, Yasuoka and Terauchi, 2014]—measure the attacker's ability to distinguish some secret values from

OOPSLA '21, Chicago, IL

others. Those metrics do not accommodate declassification or leakage interpretability, our main concerns here.

**Declassification.** To rule out allowed leakage and focus on targeted leakage, information flow control research supports declassification policies to specify the secret information permitted to transfer to observable variables (e.g., Banerjee et al. [2008], Chong and Myers [2004], Ferraiuolo et al. [2017], Giacobazzi and Mastroeni [2018], McCall et al. [2018], Sabelfeld and Myers [2003], Sabelfeld and Sands [2009]). However, while this work omits declassified information from its analysis, it does not quantitatively measure the remaining leakage in light of what the attacker can already infer from the declassified information. In contrast, our work adapts information leakage measurement to account for such inferences.

Leakage interpretability. To interpret quantitative leakage, domain-specific works (e.g., SPEECH-MINER [Xiao et al., 2020], CACHEBAR [Zhou et al., 2016]) use customized measures following a specific attack templates, forgoing general measures. Although those customized measures are more understandable when interpreting a specific attack vector, they are blind to leakage from different attacks not considered. One crucial improvement our work makes in evaluating information leakage is to generate an interpretable model to explain how leakage occurs. Already an emerging topic in machine learning (e.g., Chen et al. [2018], Molnar [2019]), interpretability is especially important in security evaluation, since it is not easy to draw a clear threshold to indicate when a system is secure enough, even with a perfect measure. Many methods for measuring leakage in software (e.g., Chattopadhyay and Roychoudhury [2018], Godefroid et al. [2012], Wang et al. [2009], Zhou et al. [2018]) generate a code path to help the analyst understand leakage. However, leakage in hardware-software joint codebases often exploits interactions between the two, which can manifest in many code-dependent paths. We are aware of no comparable work that explores an interpretable ML model to explain information-flow leakage, though the method we use to extract explanations in Sec. 4.3 builds from previous work in interpretable ML (e.g., Friedman and Popescu [2008], Ribeiro et al. [2016, 2018]).

# **3 NONINTERFERENCE AND DECLASSIFICATION**

We begin in Sec. 3.1 by providing background on the noninterference measurement methodology of Zhou et al. [2018]. We then discuss how we extend this methodology to support declassification, our first contribution, in Sec. 3.3.

# 3.1 Background on noninterference measure

To analyze the leakage from a procedure  $proc^1$ , the procedure is modeled as having four different sets of formal parameters: a set  $Vars_{\bar{s}}$  of secret input variables; a set  $Vars_{\bar{c}}$  of attacker-controlled input variables; a set  $Vars_{\bar{t}}$  of other input variables; and a set  $Vars_{\bar{o}}$  of attacker-observable output variables. The actual parameter values assigned to those variables in an invocation of *proc* are given by maps  $\vec{s} : Vars_{\bar{s}} \rightarrow Vals_{\bar{s}}$ ,  $\vec{c} : Vars_{\bar{c}} \rightarrow Vals_{\bar{c}}$ , and  $\vec{i} : Vars_{\bar{t}} \rightarrow Vals_{\bar{t}}$ , respectively; e.g.,  $\vec{i}(ivar) \in Vals_{\bar{t}}$  represents the value passed in variable  $ivar \in Vars_{\bar{t}}$ . The attacker-observable outputs of the procedure are defined by the map  $\vec{o} : Vars_{\bar{o}} \rightarrow Vals_{\bar{o}}$ . Accordingly, we denote the procedure

$$\vec{o} \leftarrow proc(\vec{c}, \vec{i}, \vec{s})$$

We assume that *proc* is deterministic; a nondeterministic *proc* can be rendered deterministic by providing the random values as inputs, say  $\vec{i}$  ('coins'). A given *proc* can then be characterized by a

<sup>&</sup>lt;sup>1</sup>Different from the definition used by Zhou et al. [2018], which is for a software procedure, our *proc* ( $\vec{c}$ ,  $\vec{i}$ ,  $\vec{s}$ ) includes both the software and hardware logic.

logical postcondition  $\Pi_{proc}(\vec{c}, \vec{o}, \vec{i}, \vec{s})$  that constrains how the values in  $\vec{o}$  relate to those in  $\vec{c}$ ,  $\vec{i}$ , and  $\vec{s}$  in any execution. Without loss of generality, below we assume  $Vars_{\vec{s}}$  contains a single variable *svar*, i.e.,  $Vars_{\vec{s}} = \{svar\}$ .

The basic idea of the metric developed by Zhou et al. [2018] is to quantify the difficulty the attacker has in distinguishing between  $\vec{s}(svar) \in S$  and  $\vec{s}(svar) \in S'$  for random, disjoint sets S, S', based on the  $\langle \vec{c}, \vec{o} \rangle$  pairs possibly available to it in the two cases, denoted  $Y_S, Y_{S'}$ , i.e.,

$$X_{S} = \left\{ \langle \vec{c}, \vec{o}, \vec{i} \rangle \mid \exists \vec{s} : \Pi_{proc}(\vec{c}, \vec{o}, \vec{i}, \vec{s}) \land \vec{s}(svar) \in S \right\}$$

$$Y_{S} = \left\{ \langle \vec{c}, \vec{o} \rangle \mid \exists \vec{i} : \langle \vec{c}, \vec{o}, \vec{i} \rangle \in X_{S} \right\}$$

Zhou et al. [2018] specifically explored the Jaccard distance between  $Y_S$  and  $Y_{S'}$  to measure the difficulty an attacker would have in distinguishing between  $\vec{s}(svar) \in S$  and  $\vec{s}(svar) \in S'$ . To better capture the importance of  $\vec{i}$  in the leakage, however, they further replaced  $Y_S \cap Y_{S'}$  with  $\hat{X}_{S,S'}$ , where<sup>2</sup>

$$\begin{split} \check{X}_{S,S'} &= X_S \cup X_{S'} \\ \hat{X}_{S,S'} &= \left\{ \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\mathbf{l}} \rangle \left| \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\mathbf{l}} \rangle \in \check{X}_{S,S'} \land \langle \vec{\mathbf{c}}, \vec{\mathbf{o}} \rangle \in Y_S \cap Y_{S'} \right\} \end{split}$$

In this way, the number of values  $\vec{i}$  for  $\langle \vec{c}, \vec{o} \rangle$  exposed in  $\hat{X}_{S,S'}$  serves as the "weight" of that  $\langle \vec{c}, \vec{o} \rangle$  pair. When  $\langle \vec{c}, \vec{o}, \vec{i} \rangle$  is from

$$\tilde{X}_{S,S'} = \check{X}_{S,S'} \setminus \hat{X}_{S,S'} \tag{1}$$

an attacker can distinguish if  $\vec{s}(svar)$  is from *S* or *S'*. Zhou et al. [2018] thus suggested the measure  $\hat{J}_n$ , where

$$\hat{J}(S,S') = \left| \tilde{X}_{S,S'} \right| / \left| \check{X}_{S,S'} \right| = 1 - \left| \hat{X}_{S,S'} \right| / \left| \check{X}_{S,S'} \right|$$

(2)

$$\hat{J}_n = \underset{\substack{S, S' : |S| = |S'| = n \\ \land S \cap S' = \emptyset}}{\operatorname{avg}} \hat{J}(S, S')$$

(3)

As discussed by Zhou et al. [2018, Sec. III], when *n* is small,  $\hat{J}_n$  measures how frequently leakage occurs, whereas when *n* is large, it measures how much information about the secret leaks, when leakage occurs.

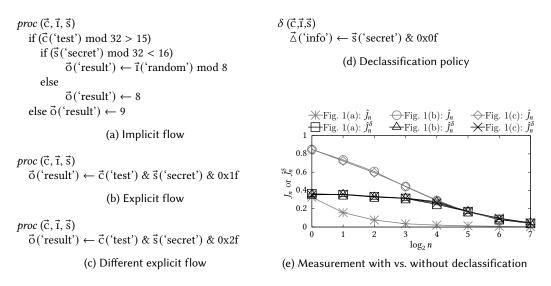

#### 3.2 Motivating examples

To see this measure applied to simple programs, consider the two programs with a secret shown in Fig. 1(a) and Fig. 1(b). The procedure in Fig. 1(a) returns a random value between 0-7 or a fixed value 8 depending on whether  $\vec{s}$  ('secret') mod 32 < 16 if  $\vec{c}$  ('test') mod 32 > 15 and returns a fixed value 9 otherwise. The second procedure in Fig. 1(b) returns the five least significant bits of  $\vec{s}$  ('secret') &  $\vec{c}$  ('test'). Directly measuring the two procedures using  $\hat{J}_n$  leads to different leakage measures, as it should, as shown in Fig. 1(e).

Some sources of information leakage may be inevitable or intentional; e.g., a bank website may not mask the last four digits of a user's social security number when displaying it to her browser, and so the site intentionally "leaks" that portion to a malicious browser. In the context of the preceding example, now suppose the leakage of the four least significant bits of the secret is intended (similar to the SSN example). Since the  $\hat{J}_n$  curve only reflects the total interference, including the portion *intended* to leak (i.e., the four least significant bits), the  $\hat{J}_n$  curves shown in Fig. 1(e) mislead us to

<sup>&</sup>lt;sup>2</sup>Our definition of  $\hat{X}_{S,S'}$  differs from Zhou et al. [2018], which only requires  $\langle \vec{c}, \vec{o}, \vec{i} \rangle \in X_S$ . Ours has the same essential properties but is symmetric with respect to *S* and *S'* and so is easier to work with.

OOPSLA '21, Chicago, IL

Ziqiao Zhou and Michael K. Reiter

Fig. 1. Motivating examples for declassification (Sec. 3.3) and interpretation (Sec. 4)

conclude that Fig. 1(a) is more secure than Fig. 1(b). In truth, they both additionally leak the fifth least significant bit, which is the only leakage that matters.

#### 3.3 Declassification

To exclude such intended leakage from the analysis, it will be helpful to provide a method to exempt some identified information leakages specified by the analyst, allowing the analysis to focus on the leakage that remains. Specifically, our methodology seeks to assess the degree to which a procedure permits secrets to be distinguished by the attacker using attacker-observable and declassified information but not by the declassified information alone.

Let  $\vec{\Delta} \leftarrow \delta(\vec{c}, \vec{i}, \vec{s})$  denote the allowed information exposure (e.g., for a website requiring SSN,  $\vec{\Delta}$  is the last four digits), and let

$$\Pi_{proc\,\delta}(\vec{c},\vec{o},\vec{\Delta},\vec{i},\vec{s}) \leftarrow \Pi_{proc}(\vec{c},\vec{o},\vec{i},\vec{s}) \wedge \Pi_{\delta}(\vec{c},\vec{\Delta},\vec{i},\vec{s})$$

where  $\Pi_{\delta}(\vec{c}, \vec{\Delta}, \vec{i}, \vec{s})$  is a logical postcondition for  $\delta$  that relates  $\vec{\Delta}$  to  $\vec{c}, \vec{i}$ , and  $\vec{s}$ . Then, we can define the attacker's accessible set  $Y_S^{\delta}$  of  $\langle \vec{c}, \vec{o}, \vec{\Delta} \rangle$  tuples and allowed accessible set  $D_S^{\delta}$  consistent with chosen secret set S by

$$\begin{split} X_{S}^{\delta} &= \left\{ \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta}, \vec{\mathbf{1}} \rangle \left| \exists \vec{\mathbf{s}} : \vec{\mathbf{s}} (svar) \in S \land \Pi_{proc,\delta} (\vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta}, \vec{\mathbf{1}}, \vec{\mathbf{s}}) \right\} \\ Y_{S}^{\delta} &= \left\{ \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta} \rangle \left| \exists \vec{\mathbf{1}} : \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta}, \vec{\mathbf{1}} \rangle \in X_{S}^{\delta} \right\} \\ D_{S}^{\delta} &= \left\{ \langle \vec{\mathbf{c}}, \vec{\Delta} \rangle \left| \exists \vec{\mathbf{o}}, \vec{\mathbf{1}} : \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta}, \vec{\mathbf{1}} \rangle \in X_{S}^{\delta} \right\} \end{split}$$

Since the declassified information is allowed to leak, we are concerned only with cases where the secret is distinguishable by  $\langle \vec{c}, \vec{o}, \vec{\Delta} \rangle$  but not by  $\langle \vec{c}, \vec{\Delta} \rangle$ . Here, we define a set  $\tilde{X}^{\delta}_{S,S'}$  to include the

OOPSLA '21, Chicago, IL

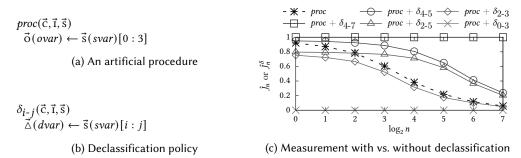

Fig. 2. Declassification example

tuples  $\langle \vec{c}, \vec{0}, \vec{\Delta} \rangle$  that leak whether the secret is in *S* or *S'*, assuming  $\langle \vec{c}, \vec{\Delta} \rangle$  is equivalent.

$$\check{X}^{\delta}_{S,S'} = \left\{ \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\boldsymbol{\Delta}}, \vec{\mathbf{I}} \rangle \middle| \begin{array}{l} \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\boldsymbol{\Delta}}, \vec{\mathbf{I}} \rangle \in X^{\delta}_{S} \cup X^{\delta}_{S'} \\ \wedge \quad \langle \vec{\mathbf{c}}, \vec{\boldsymbol{\Delta}} \rangle \in D^{\delta}_{S} \cap D^{\delta}_{S'} \end{array} \right\}$$

$$(4)$$

$$\hat{X}^{\delta}_{S,S'} = \left\{ \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta}, \vec{\mathbf{i}} \rangle \middle| \begin{array}{c} \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta}, \vec{\mathbf{i}} \rangle \in \check{X}^{\delta}_{S,S'} \\ \wedge \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta} \rangle \in Y^{\delta}_{S} \cap Y^{\delta}_{S'} \end{array} \right\}$$

(5)

$$\tilde{X}^{\delta}_{S,S'} = \check{X}^{\delta}_{S,S'} \setminus \hat{X}^{\delta}_{S,S'} \tag{6}$$

Thus, we can use an alternative metric

$$\hat{J}^{\delta}(S,S') = \left| \tilde{X}^{\delta}_{S,S'} \right| / \left| \check{X}^{\delta}_{S,S'} \right|$$

(7)

$$\hat{S}_{n}^{\delta} = \arg_{\substack{S,S': |S| = |S'| = n \\ A \leq S \leq S' = \emptyset}} \hat{J}^{\delta}(S,S')$$

(8)

Returning to the examples in Fig. 1(a) and Fig. 1(b) with declassification of the four least significant bits (Fig. 1(d)), the  $\hat{J}_n^{\delta}$  curves show the same quantitative leakage (Fig. 1(e)), as they should.

To further illustrate the the impact of declassification, consider the simple procedure shown in Fig. 2(a). In this procedure,  $\vec{s}(svar)$  is an 8-bit value, and proc outputs the lowest 4 bits as  $\vec{o}(ovar)$ . The declassification policy shown in Fig. 2(b) allows the *i*-th to *j*-th bits of  $\vec{s}(svar)$  to be released. We evaluate  $\hat{J}_n^{\delta}$  with differently parameterized declassification policies in Fig. 2(c). Specifically, when the lowest 4 bits (i = 0, j = 3) are declassified, then the additional leakage from *proc* is nothing, which is demonstrated by the "proc +  $\delta_{0-3}$ " curve. When the declassification policy declassifies all but the lowest 4 bits (i = 4, j = 7), then the additional leakage by *proc* is maximized, as shown by the "proc +  $\delta_{4-7}$ " curve. Intuitively, if  $\vec{o}(ovar)$  and  $\vec{\Delta}(dvar)$  do not overlap (e.g., "proc +  $\delta_{4-7}$ ") and "proc +  $\delta_{4-5}$ "), then the  $\hat{J}_n^{\delta}$  curve should be higher than  $\hat{J}_n$ , whereas if  $\vec{o}(ovar)$  includes all of  $\vec{\Delta}(dvar)$  (e.g., "proc +  $\delta_{0-3}$ " and "proc +  $\delta_{0-1}$ "), then  $\hat{J}_n^{\delta}$  should be lower than  $\hat{J}_n$ . A hybrid case occurs when  $\vec{o}(ovar)$  includes a portion of  $\vec{\Delta}(dvar)$  (e.g., "proc +  $\delta_{2-5}$ "), where  $\hat{J}_n^{\delta}$  is lower than  $\hat{J}_n$  when n is small but becomes larger when n is large. This is consistent with the interpretation that  $\hat{J}_n^{\delta}$  with small *n* primarily reflects the number of secret values for which interference occurs [Zhou et al., 2018]; e.g., when n = 1, two secret values share bits 0-1 (and so cannot be distinguished by bits 0-3 after declassifying bits 2-5) in 25% of cases, but share bits 0-3 (and so cannot be distinguished using them) in only 6.25% of cases. Larger *n*, in contrast, better reflects the amount of leakage that occurs [Zhou et al., 2018]. For example, in a random partition of all  $2^8$  values into sets S and S' of equal size (i.e.,  $n = 2^7$ ), every value for bits 2–5 is represented in both S and S' with high probability. In conjunction with the additional bits 0-1 output in  $\vec{0}$  (yielding six bits of the secret value in total), however, these bits give the attacker greater distinguishing power than do bits 0-3 alone.

### 4 INTERPRETING LEAKAGE

Our metric measures the additional interference of a secret with values observable by the attacker, beyond that implied by declassified information. For this to be useful to an analyst, however, we need to explain *how* this leakage occurs. Specifically, while the conditions under which leakage occurs are already present in the procedure postcondition, it is difficult to understand the formula without further help (e.g., see Sec. 6.5).

#### 4.1 Motivating examples for interpretation

Consider again the motivating examples in Fig. 1(a) and Fig. 1(b). The two procedures own quite different outputs but still leak the same additional information about the secret after declassification (i.e., both leak the fifth least significant bit of the secret when  $\vec{c}$  ('test')'s fifth bit is 1 and nothing otherwise). To cut through the differences in code style and concrete values, DINOME derives the condition when a pair of secrets are distinguishable using paired samples of input. Thus, the interference rule for both cases becomes  $|\vec{s}('secret')[4] - \vec{s}'('secret')[4]| > 0 \land \vec{c}('test')[4] = 1$ . This rule shows the equivalence of these procedures' leakages after declassification.

In addition, interpreting leakage can differentiate cases with the same *amount* of leakage but different conditions in which that leakage occurs. For example, the procedure in Fig. 1(c), which reveals the four least significant bits and the sixth bit of the secret when the sixth bit of  $\vec{c}$  ('test') is 1, leaks the same amount of information about a different portion of the secret under a different attack condition. A quantitative leakage measurement with the same four low-order bits declassified will not distinguish Fig. 1(c) from Fig. 1(b) (see Fig. 1(e)). Through DINoMe's interpretation, we provide a slightly different interference rule for Fig. 1(c), however:  $|\vec{s}$  ('secret')[5]  $-\vec{s}'$  ('secret')[5]| >  $0 \land \vec{c}$  ('test')[5] = 1.

Though these motivating examples seem small and readable even when using different coding styles and output values, real-world code can become difficult to understand, particularly when spanning different levels of abstraction (e.g., a processor and the code it is executing). It is here we expect our interpretation of interference to simplify investigating leakage. Learning from the previous examples, our interpretation should achieve two goals. First, the interference interpretation for the same functionality should be consistent no matter how the functionality is implemented. Second, the interference interpretation should distinguish two procedures if they leak information in different ways, even when they leak the same amount.

#### 4.2 Noninterference and interference tuples

Our first step toward providing an intuitive explanation for the leakage that occurs is to train a binary classifier to classify 4-tuples  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle$  into those that illustrate leakage occurring (i.e., that permit the attacker to distinguish  $\vec{s}(svar)$  and  $\vec{s}'(svar)$  from the resulting output  $\vec{o}$ ) and those that do not. When using declassification, the interference tuples should only include those where the secrets can be distinguished using  $\vec{c}, \vec{o}, \vec{\Delta}$  but not using just  $\vec{c}, \vec{\Delta}$ .

More specifically, we define the interference set *IS* based on (6). That is, when the attacker chooses  $\vec{c}$ , if an observable value is feasible for  $\langle \vec{i}, \vec{s} \rangle$  for some  $\vec{i}$  but is never possible for  $\langle \vec{i}', \vec{s}' \rangle$  for any  $\vec{i}'$  that shares a declassification value with  $\langle \vec{i}, \vec{s} \rangle$ , then  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle$  is added to *IS*:

$$IS = \left\{ \langle \vec{\mathbf{c}}, \vec{\mathbf{i}}, \vec{\mathbf{s}}, \vec{\mathbf{s}}' \rangle \middle| \exists \vec{\mathbf{o}}, \vec{\Delta} : \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta}, \vec{\mathbf{i}} \rangle \in X_S^{\delta} \land \langle \vec{\mathbf{c}}, \vec{\Delta} \rangle \in D_{S'}^{\delta} \cap D_{S'}^{\delta} \land \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta} \rangle \in Y_S^{\delta} \setminus Y_{S'}^{\delta} \right\}$$

(9)

where  $S = \{\vec{s}(svar)\}$  and  $S' = \{\vec{s}'(svar)\}$ .

The noninterference set *NS* should include two types of tuples. For an attacker-chosen  $\vec{c}$ , if there is a observable value  $\vec{o}$  that is feasible for an  $\langle \vec{i}, \vec{s} \rangle$  pair and an  $\langle \vec{i}', \vec{s}' \rangle$  pair, tuple  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle$  belongs to *NS* as it is an example where no interference occurs. In addition, for an attacker-chosen  $\vec{c}$ , if there is a declassification value  $\vec{\Delta}$  that is feasible for  $\langle \vec{i}, \vec{s} \rangle$  but not  $\langle \vec{i}', \vec{s}' \rangle$  for any  $\vec{i}'$ , then  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle$  should also be added to *NS*, as  $\vec{s}$  and  $\vec{s}'$  can already be distinguished using the declassified value:

$$NS = \left\{ \langle \vec{c}, \vec{1}, \vec{s}, \vec{s}' \rangle \middle| \exists \vec{o}, \vec{\Delta} : \langle \vec{c}, \vec{o}, \vec{\Delta}, \vec{1} \rangle \in X_S^{\delta} \land \langle \vec{c}, \vec{o}, \vec{\Delta} \rangle \in Y_S^{\delta} \cap Y_{S'}^{\delta} \right\} \\ \cup \left\{ \langle \vec{c}, \vec{1}, \vec{s}, \vec{s}' \rangle \middle| \exists \vec{o}, \vec{\Delta} : \langle \vec{c}, \vec{o}, \vec{\Delta}, \vec{1} \rangle \in X_S^{\delta} \land \langle \vec{c}, \vec{\Delta} \rangle \in D_S^{\delta} \setminus D_{S'}^{\delta} \right\}$$

(10)

where  $S = {\vec{s}(svar)}$  and  $S' = {\vec{s}'(svar)}$ .

Since *NS* and *IS* are large in practical scenarios, enumerating all tuples is generally infeasible. Instead, we generate samples in each set to train a machine learning model, from which explanations of the leakage will be extracted (as described below). Doing so with modern SAT solvers, however, typically results in samples that cover *NS* and *IS* unevenly, since solvers generally enumerate the next solution by simply adding a conflict constraint to block out previous solutions; as a result, the next solution found is typically close to the previous. Another drawback of using this "blocking" method to sample is that we cannot parallelize the sampling.

For this reason, we sample from *NS* and *IS* using hash-based sampling (cf., Zhou et al. [2018]). Specifically, we sample a limited number of solutions by adding a random universal hashing constraint to the formula given to the solver. Due to the hash function's universality, we can run multiple samplers in parallel to generate a large number of uniformly distributed solutions. In most cases, the sizes of the sampled sets  $\hat{NS}$  and  $\hat{IS}$  differ either due to differences in the sizes of *NS* and *IS* or due to the solving difficulty of one set compared to the other. We associate a sample weight to each element so the weight of each set is equal in the training process described below.

#### 4.3 Interpretation through a rule-based method

Given  $\hat{NS}$  and  $\hat{IS}$ —i.e.,  $\langle \vec{c}, \vec{1}, \vec{s}, \vec{s}' \rangle$  tuples labeled according to whether they illustrate noninterference or interference—we could train an interpretable machine-learning model and then extract rules to explain to the user what gives rise to interference. A natural such model to consider is a decision tree. In a decision tree, each decision node (i.e., interior node) is a predicate on features of a  $\langle \vec{c}, \vec{1}, \vec{s}, \vec{s}' \rangle$ tuple, and its two children correspond to a true or false evaluation of this predicate on a tuple, respectively. A  $\langle \vec{c}, \vec{1}, \vec{s}, \vec{s}' \rangle$  tuple is classified by traversing the tree from its root, following the branch from each decision node corresponding to the result of evaluating the predicate at that node on the tuple. Each leaf is labeled with an estimate of the probability that a tuple constrained by the predicates' evaluations from the root to that leaf is in *IS*. We will discuss what features we include in the process of building decision trees in Sec. 4.4, but an example might be individual variables (e.g.,  $\vec{c}$  (*cvar*)).

A single decision tree can easily grow to be deep and complex, and it can miss some useful combinations of predicates since each decision predicate is highly influenced by the splits above it in the tree. To make the decision tree model more powerful in finding useful predicates, we used a decision-tree ensemble called gradient boosted trees [Friedman, 2001]. This process produces *m* trees denoted  $T_1, \ldots, T_m$ , with associated weights. If we denote by  $T_j(\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle)$  the real number stored at the leaf to which  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle$  is assigned by  $T_j$ , then the weighted sum of  $T_j(\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle)$  for  $j = 1, \ldots, m$  is an estimate of the probability that  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle \in IS$ .

To interpret tree ensembles, rule-based classifiers (e.g., RuleFit [Friedman and Popescu, 2008], Slipper [Cohen and Singer, 1999], Pre [Fokkema, 2020]) were introduced to bridge the interpretability of a decision tree with the modeling power of a tree ensemble. Our toolchain leverages SKOPE-RULES (https://skope-rules.readthedocs.io/) to generate logical rules from the tree ensemble. Specifically, consider any path from the root to a leaf in a tree  $T_j$ , and let  $\pi_{j,1}, \ldots, \pi_{j,\ell}$  denote the predicates along that path that evaluated to true. So, for example, if the first predicate encountered in  $T_j$ , say " $\vec{c}(cvar) = 1$ ", evaluated to false, then  $\pi_{j,1} = \vec{c}(cvar) \neq 1$ ". Then, SKOPE-RULES constructs a rule by conjoining  $\pi_{j,1}, \ldots, \pi_{j,\ell}$ , with the caveat that it limits the number of predicates included in any rule by heuristically pruning them.

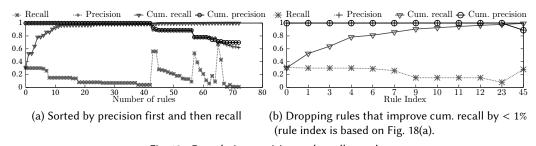

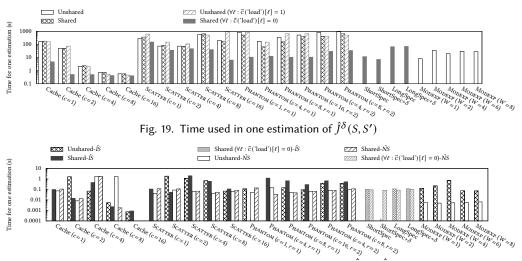

Each such rule has a *precision* and *recall*, which we evaluate using a validation set held out from  $\hat{NS}$  and  $\hat{IS}$  during training. That is, the *recall* of a rule is the fraction of validation samples held out from  $\hat{IS}$  for which the rule evaluates to true, and its *precision* is the fraction of validation samples (from  $\hat{IS}$  or  $\hat{NS}$ ) for which the rule evaluates to true that were held out from  $\hat{IS}$ . We further prune rules by iteratively removing conjuncts from a long rule if the precision of the resulting rule is at least 95% of the original. We then rank order rules according first to precision, and then according to recall.

#### 4.4 Feature engineering

The utility of the rule generation described in the previous section depends critically on the features of each  $\langle \vec{c}, \vec{1}, \vec{s}, \vec{s}' \rangle$  tuple exposed when training the tree ensemble, from which the predicates making up the decision nodes of each tree are formed. One factor that makes feature engineering especially critical here is that the SAT solver used to produce elements of  $\hat{IS}$  and  $\hat{NS}$  requires that the conditions defining IS and NS (i.e., conditions (9) and (10))

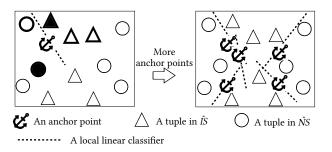

Fig. 3. Finding linear combinations of features near anchor points

be presented to the SAT solver in terms of binary variables only. As such, each solution generated by the SAT solver is expressed as an assignment to these binary variables. While for some hardware logic, a binary representation of the relevant variables is most natural, for other types of logic (e.g., on integers), it is not. For this reason, we augment each binary solution returned by the SAT solver (i.e., each  $\langle \vec{c}, \vec{1}, \vec{s}, \vec{s'} \rangle$  tuple) with additional features.

- **Type-aware features:** First, we reconstruct features in a type-aware way from their binary representations. For example, if a variable was initially an integer before being reduced to a collection of binary variables in the formula presented to the SAT solver, we recover the integer value from the bit-vector solution and include it as a feature on which the tree ensemble can trained. With such type-aware features, predicates such as, e.g.,  $\vec{s}(svar) < 15$  can be learned in a search for simple predicates testing only a single feature, i.e., unary predicates.

- Symmetric features: Due to the symmetry of  $\vec{s}$  and  $\vec{s}'$ , an interference rule could be trivially transformed to another valid interference rule by exchanging  $\vec{s}$  and  $\vec{s}'$ . For example, when a rule is  $\vec{s}(svar)[0] = 0 \land \vec{s}'(svar)[0] = 1$ , there must be a rule  $\vec{s}(svar)[0] = 1 \land \vec{s}'(svar)[0] = 0$ . Thus, we create  $|\vec{s}(svar)[i] \vec{s}'(svar)[i]|$  for each bit *i* in secret.

- Linear combinations of multiple variables: Unary predicates, however, will be unable to naturally capture some relationships resulting in leakage. For example, if leakage happens only when  $\vec{s}(svar) > \vec{c}(cvar)$ , permitting only unary predicates will result in a boundary characterized point-by-point, e.g., " $\vec{s}(svar) \ge \theta \land \vec{c}(cvar) < \theta$ " where  $\theta = 1, 2, ...$  We thus expanded our feature

Fig. 4. DINoMe workflow

set to permit linear combinations of some features (e.g.,  $\vec{s}(svar) - \vec{c}(cvar)$ ), chosen by a linear classifier.

To accommodate branching in the procedure that results in discontinuities in the boundary between sample sets  $\hat{IS}$  and  $\hat{NS}$ , we opted for a *local* linear classifier (e.g., Fan [1993], Ribeiro et al. [2018]). That is, we pick *anchor points*, around each of which we train a local classifier that best separates the *nearby* samples in  $\hat{IS}$  and  $\hat{NS}$ . (See Fig. 3.) To select anchor points, we first find pairs of  $\langle \vec{C}, \vec{I}, \vec{S}, \vec{S'} \rangle$  tuples, one from  $\hat{IS}$  and one from  $\hat{NS}$ , that are *neighbors* in one feature (i.e., after ranking all tuples by this feature, the pair are adjacent in the ranking) and then take the pair's *midpoint* tuple as their per-feature means. We select anchors uniformly at random from these midpoints. For each anchor, we train a linear classifier using the tuples in  $\hat{IS}$  and  $\hat{NS}$  that are within a threshold Euclidean distance from the anchor. The linear combination of features used in this linear classifier is then added as another feature to each  $\langle \vec{C}, \vec{I}, \vec{S}, \vec{S'} \rangle$  tuple.

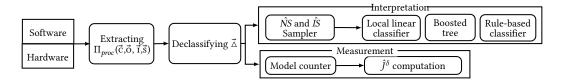

#### **5** IMPLEMENTATION

We developed  $DINOME^3$  for evaluating and interpreting leakage, described in Sec. 3–4, with an eye toward applying it to evaluate and understand leakage from hardware designs. Though our declassification and interpretation methodologies are not limited to hardware designs, we believe they will be most useful in complicated cases where developers need to understand the interactions between low-level and high-level code. To capture such cases, we define the procedure proc to be a hardware design, say written in Verilog, in its initial state but with a predefined program stored in its memory. DINOME enables the user to annotate the configuration by marking components of the hardware state as attacker-controlled (i.e., in  $Vars_{\vec{c}}$ ), attacker-observable (in  $Vars_{\vec{o}}$ ), secret (in  $Vars_{\vec{s}}$ ), or otherwise unknown to the attacker (in Vars;). DINOME workflow for analyzing this "procedure" is illustrated in Fig. 4. Our system converts this "procedure," which we continue to denote proc, to a cycle-accurate logical formula  $\Pi_{proc}$  that characterizes hardware execution of the program and that relates  $\vec{c}$ ,  $\vec{o}$ ,  $\vec{i}$ , and  $\vec{s}$ . The user can also declare a declassification function  $\delta$  that operates on the hardware state of the system (we will give examples below), from which DINOME similarly produces a logical formula  $\Pi_{\delta}$  that characterizes how the declassified information  $\vec{\Delta}$  relates to inputs  $\vec{c}$ ,  $\vec{i}$ , and  $\vec{s}$  in the execution of *proc*. From  $\Pi_{proc}$  and  $\Pi_{\mathcal{S}}$  DINOME generates  $\hat{J}_n^{\delta}$  for varying n (see (8)) and, if requested, sample sets  $\hat{IS}$  and  $\hat{NS}$  from IS (see (9)) and NS (see (10)), respectively. These sets seed the generation of the rules for interpreting leakage, as discussed in Sec. 4.

Below we discuss particular challenges we encountered when building DINoME and how we overcame them. We focus on how to extract  $\Pi_{proc}(\vec{c}, \vec{o}, \vec{i}, \vec{s})$  in Sec. 5.1. In Sec. 10.1, we describe simplification techniques we leverage as a preprocessing step before performing projected model counting, described in Sec. 5.2. Finally, we discuss our technique for sampling to create  $\hat{IS}$  and  $\hat{NS}$  in Sec. 5.3.

<sup>&</sup>lt;sup>3</sup>https://github.com/DINoMe-Project/DINoMe

#### 5.1 Extracting $\prod_{proc} (\vec{c}, \vec{o}, \vec{i}, \vec{s})$

To analyze the leakage from *proc*, we need an accurate postcondition  $\Pi_{proc}(\vec{c}, \vec{o}, \vec{1}, \vec{s})$  for *proc*. In practice, generating a postcondition for an arbitrary procedure is not trivial. Especially here, where our concern is detecting leakage from a processor implementation when running an application—i.e., the procedure *proc* includes numerous cycles of a cycle-accurate implementation of the processor logic as well as the software logic—the postcondition will be quite large.

Our general strategy to construct  $\Pi_{proc}(\vec{c}, \vec{o}, \vec{1}, \vec{s})$  in these circumstances is to assemble it one cycle at a time. Yosys [Wolf] provides a framework to convert the Verilog code for a processor design to its internal register-transfer level (RTL) intermediate language, optimize or modify the design using a series of passes, and finally translate the design to targeted formula through its back-end pass. The SMT2 back-end pass defines a data structure for each hardware module representing the module's temporary hardware state, a function to implement the module's state transition from one cycle to the next, and an initialization function to initialize the module's state. To incorporate the software logic of *proc*, we compile the software to its hardware-readable assembly and load the assembly into the instruction memory unit.

To mark the symbolic variables, the analyst defines a configuration file to mark as symbolic each input parameter of *proc* (in this case, *svar*, *ivar*, and *cvar*), which can be a software variable located at a fixed location in the memory unit or a wire/register inside the hardware module. Our modified SMT2 backend pass in Yosys then tracks the constraints associated with this symbolic data throughout a cycle execution. Specifically, it outputs a logical postcondition  $\tau_{proc}(\vec{H}^{t-1}, \vec{H}^t)$ that relates fully symbolized hardware state  $\vec{H}^{t-1}$ :  $Vars_{\vec{H}} \rightarrow Vals_{\vec{H}}$  at the end of cycle t - 1 to the hardware state  $\vec{H}^t$  that results from executing cycle t. Since the hardware state includes memory units, registers, etc.,  $\tau_{proc}(\vec{H}^{t-1}, \vec{H}^t)$  with fully symbolized  $\vec{H}^{t-1}$  is too large to naively extend to cover multiple cycles. We also use the pass to generate initialization logic  $\Psi_{proc}^0(\vec{c}, \vec{i}, \vec{s}, \vec{H}^0)$  that concretely characterizes the first-cycle starting state  $\vec{H}^0$  (upon a reset) except for the configured symbolic inputs *svar*, *ivar*, and *cvar*.

Using the transition logic, we construct a cycle-accurate postcondition  $\Psi_{proc}^{T}$  representing the logic between symbolic inputs and its internal hardware state one cycle at a time, leveraging the entire hardware state as an "observable" output of the cycle.

$$\Psi_{proc}^{T}(\vec{c},\vec{i},\vec{s},\vec{H}^{T}) \leftarrow \Psi_{proc}^{0}(\vec{c},\vec{i},\vec{s},\vec{H}^{0}) \wedge \bigwedge_{t=1}^{T} \tau_{proc}(\vec{H}^{t-1},\vec{H}^{t})$$

We finally define  $\Pi_{proc}(\vec{c}, \vec{o}, \vec{i}, \vec{s})$  by defining  $\vec{o}$  in terms of the sequence of hardware states  $\langle \vec{H}^t \rangle_{t=0}^T$  using a formula  $\Gamma(\langle \vec{H}^t \rangle_{t=0}^T, \vec{o})$ .

$$\Pi_{proc}(\vec{c},\vec{o},\vec{i},\vec{s}) \leftarrow \Psi_{proc}^{T}(\vec{c},\vec{i},\vec{s},\vec{H}^{T}) \wedge \Gamma(\langle \vec{H}^{t} \rangle_{t=0}^{T},\vec{o})$$

(11)

For example, in cache-based side channels, the observable parameters are whether there is a cache hit/miss during the execution, which is constructed using the values of the *s2\_hit* register across the execution (as demonstrated in Sec. 6.2).

Applying a correct combination of techniques to simplify  $\Pi_{proc}(\vec{c}, \vec{o}, \vec{i}, \vec{s})$  is critical to scaling the sampling of *IS* and *NS* to create  $\hat{IS}$  and  $\hat{NS}$  and to count  $\left|\tilde{X}^{\delta}_{S,S'}\right|$  and  $\left|\tilde{X}^{\delta}_{S,S'}\right|$  to compute  $\hat{J}^{\delta}_{n}$ . We defer discussion of these simplifications to Appendix 10.1.

To correctly measure leakage, the postcondition for *proc* must be complete and sound. Completeness means that if  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{o} \rangle$  is feasible for *proc*, then  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{o} \rangle$  satisfies  $\Pi_{proc}(\vec{c}, \vec{o}, \vec{i}, \vec{s})$ . Soundness means that if  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{o} \rangle$  is infeasible for *proc*, then  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{o} \rangle$  does not satisfy  $\Pi_{proc}(\vec{c}, \vec{o}, \vec{i}, \vec{s})$ . Here,

$\Pi_{proc}(\vec{c}, \vec{o}, \vec{i}, \vec{s})$  is derived from the hardware transition logic  $\tau_{proc}$ . Since  $\tau_{proc}$  represents how the next hardware state is derived from the previous hardware state<sup>4</sup> and is derived from the actual hardware design, our postcondition is consistent with the real verilog code, provided that the Yosys SMT2 backend pass is correct.

In our experiments, we selected *T* to ensure the termination of the execution, based on our knowledge gained by studying the CPU. A more conservative method would be to track the CPU pipeline and call the SAT solver each cycle to check whether the last instruction has certainly committed. We have confirmed that adding more cycles after the termination of the execution does not affect  $\Pi_{proc}$  meaningfully, as the additional cycles do not process any valid opcodes and so only trivially change the hardware state.

#### 5.2 Measurement with declassification using projected model counting

Using CryptoMiniSAT 5.0 as the basic solver, we implemented a counter to estimate the numerator and the denominator in the measurement  $\hat{J}^{\delta}(S, S')$  in (8).

5.2.1 Computing  $\hat{J}^{\delta}(S, S')$ . To compute  $\hat{J}^{\delta}(S, S')$ , we need to count the sizes of  $\tilde{X}^{\delta}_{S,S'}$  and  $\check{X}^{\delta}_{S,S'}$ . Directly counting  $\tilde{X}^{\delta}_{S,S'}$  is not easy as the set difference operation introduces a "forall" quantifier. Fortunately, since  $|\tilde{X}^{\delta}_{S,S'}| = |\check{X}^{\delta}_{S,S'}| - |\hat{X}^{\delta}_{S,S'}|$ , it suffices to count  $\check{X}^{\delta}_{S,S'}$  and  $\hat{X}^{\delta}_{S,S'}$  for each sample pair S, S'. Intuitively, counting  $\check{X}^{\delta}_{S,S'}$  could be expressed as a projected model counting task [Aziz et al., 2015] over  $\langle \vec{c}, \vec{o}, \vec{i}, \vec{s} \rangle$  in a quantifier-free SAT problem with two copies of  $\Pi_{proc}$  shown in  $\check{F}$  below.  $\check{F}$ is translated to a CNF proposition where it uses v bit variables to represent  $\langle \vec{c}, \vec{o}, \vec{\Delta}, \vec{1} \rangle$  and others to represent  $\langle \vec{s}, \vec{s}', \vec{i}, \vec{i}' \rangle$  and auxiliary variables.

$$\check{F} \leftarrow \left(\Pi_{proc}(\vec{c}, \vec{o}, \vec{i}, \vec{s}) \vee \Pi_{proc}(\vec{c}, \vec{o}, \vec{i}', \vec{s}')\right) \land \Pi_{\delta}(\vec{c}, \vec{\Delta}, \vec{i}, \vec{s}) \land \Pi_{\delta}(\vec{c}, \vec{\Delta}, \vec{i}', \vec{s}') \land \left((\vec{s}(svar) \in S \land \vec{s}'(svar) \in S') \lor (\vec{s}'(svar) \in S \land \vec{s}(svar) \in S')\right)$$

(12)

Following Zhou et al. [2018], two random, disjoint sets *S* and *S'* of expected size *n* are specified with distinct strings  $p, \hat{p} \in \{0, 1\}^b$  where  $n = |S| / 2^b$ , and specifically with the constraint that for a fixed hash function, the hash of each  $s \in S$  is *p* and the hash of each  $s' \in S'$  is  $\hat{p}$ .

For  $\hat{X}_{S,S'}^{\delta}$ , we can define another projected model counting task over  $\langle \vec{c}, \vec{o}, \vec{\Delta}, \vec{1} \rangle$  in a quantifier-free SAT problem  $\hat{F}$  shown below.  $\hat{F}$  uses the logical postcondition  $\prod_{proc}$  twice, where the first copy is for the execution with a secret  $\vec{s}(svar) \in S$  and the second checks for existence of a secret  $\vec{s}'(svar) \in S'$  leading to a result  $\vec{o}$  also possible with  $\vec{s}$ .  $\hat{F}$  also checks the existence of some secret (denoted by  $\vec{s}''(svar)$ ) in the secret set S' leading to the equivalent declassification value  $\vec{\Delta}$  so that we can ensure the  $\vec{s}$  and  $\vec{s}'$  cannot be distinguished by  $\vec{\Delta}$ .

$$\hat{F} \leftarrow \Pi_{proc,\delta}(\vec{c}, \vec{o}, \vec{\Delta}, \vec{I}, \vec{s}) \land \vec{s}(svar) \in S$$

$$\land \Pi_{proc}(\vec{c}, \vec{o}, \vec{I}', \vec{s}') \land \vec{s}'(svar) \in S'$$

$$\land \Pi_{\delta}(\vec{c}, \vec{\Delta}, \vec{I}'', \vec{s}'') \land \vec{s}''(svar) \in S'$$

(13)

5.2.2 Optimizations for counting  $\tilde{X}^{\delta}_{S,S'}$  and  $\check{X}^{\delta}_{S,S'}$ . Enumerating all solutions to (12) and (13) using a solver is intractable. To estimate the number of solutions to each instead, we used the approximate model counting technique due to Chakraborty et al. [2013], specifically the approach taken by Soos

<sup>&</sup>lt;sup>4</sup>Unlike software, hardware code (e.g., verilog) does not use do-while loops within one cycle for which the number of iterations is determined dynamically. In our case studies, we found that the one-cycle logic for BOOM is correspondingly simple, enabling the completeness and soundness of  $\tau_{proc}$ .

E-Solver with *H* and *p* generates

$$\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}', \vec{o}, \vec{\Delta} \rangle$$

satisfying

$$\Pi_{proc,\delta}(\vec{c}, \vec{o}, \vec{\Delta}, \vec{i}, \vec{s}) \land \Pi_{proc,\delta}(\vec{c}, \vec{o}', \vec{\Delta}, \vec{i}', \vec{s}') \land \vec{o} \neq \vec{o}' \land H(\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle) = p$$

(16)

F-Solver cancels

$$\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}', \vec{o}, \vec{\Delta} \rangle$$

satisfying (16) if there is some  $\vec{i}''$  satisfying

$$\Pi_{trac \delta}(\vec{c}, \vec{o}, \vec{\Delta}, \vec{i}'', \vec{s}')$$

(17)

#### Fig. 5. Generating examples in $\hat{IS}$ using EF-solver

and Meel [2019]. That is, by specifying a randomly selected hash function  $\hat{H}^{\hat{b}} : \{0, 1\}^{v} \to \{0, 1\}^{\hat{b}}$ and an output  $\hat{p} \in \{0, 1\}^{b}$  as an additional constraint, we can estimate  $\left|\hat{X}^{\delta}_{S,S'}\right|$  using the average value of multiple estimations of  $\left|\hat{Z}^{\hat{p}}_{S,S'}\right|$  with some error  $\epsilon$  and confidence  $\delta$  (i.e.,  $\left|\hat{X}^{\delta}_{S,S'}\right| \approx \left|\hat{Z}^{\hat{p}}_{S,S'}\right| \times 2^{\hat{b}}$ ). Similarly, we could estimate  $\left|\check{X}^{\delta}_{S,S'}\right|$  using  $\check{Z}^{\check{p}}_{S,S'}$ .

$$\check{Z}^{\hat{p}}_{S,S'} = \left\{ \langle \vec{c}, \vec{o}, \vec{\Delta}, \vec{i} \rangle \middle| \langle \vec{c}, \vec{o}, \vec{\Delta}, \vec{i} \rangle \in \check{X}^{\delta}_{S,S'} \land \check{H}^{\check{b}}(\langle \vec{c}, \vec{o}, \vec{\Delta}, \vec{i} \rangle) = \check{p} \right\}$$

(14)

$$\hat{Z}_{S,S'}^{\hat{p}} = \left\{ \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta}, \vec{\mathbf{I}} \rangle \middle| \langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta}, \vec{\mathbf{I}} \rangle \in \hat{X}_{S,S'}^{\delta} \land \hat{H}^{\hat{b}}(\langle \vec{\mathbf{c}}, \vec{\mathbf{o}}, \vec{\Delta}, \vec{\mathbf{I}} \rangle) = \hat{p} \right\}$$

(15)

This optimization for model counting will limit the number of calls to the SAT solver by constraining the number of solutions available, and thus make the counting more scalable for large set size. Thus,  $\hat{J}^{\delta}(S, S')$  is estimated using the average value of  $1 - \left|\hat{Z}_{S,S'}^{\hat{p}}\right| / \left|\check{Z}_{S,S'}^{\hat{p}}\right|$  for various  $\hat{p}, \check{p}$ .

Our primary departure from the implementation by Soos and Meel [2019] lies in utilizing task-specific properties in our counting tasks to reduce redundant effort in solution searching. Specifically, since  $\hat{X}^{\delta}_{S,S'} \subseteq \check{X}^{\delta}_{S,S'}$ , we ensure that  $\hat{X}^{\delta}_{S,S'} \cap \check{Z}^{\check{p}}_{S,S'} \subseteq \hat{Z}^{\hat{p}}_{S,S'}$  in our counting by defining  $\hat{H}^{\hat{b}}(\langle \vec{c}, \vec{o}, \vec{\Delta}, \vec{1} \rangle)$  to be the  $\hat{b}$ -bit prefix of  $\check{H}^{\check{b}}(\langle \vec{c}, \vec{o}, \vec{\Delta}, \vec{1} \rangle)$  for  $\hat{b} \leq \check{b}$ . Then once we have generated solutions in  $\check{Z}^{\check{p}}_{S,S'}$ , we speed up finding solutions in  $\hat{Z}^{\hat{p}}_{S,S'}$  for  $\hat{b} = \check{b}$  (and so  $\hat{p} = \check{p}$ ) by first checking each solution in  $\check{Z}^{\check{p}}_{S,S'}$  to see if it satisfies  $\hat{F}$  (i.e., is in  $\hat{X}^{\delta}_{S,S'} \cap \check{Z}^{\check{p}}_{S,S'}$ ). Only if insufficient solutions are found with  $\hat{b} = \check{b}$  is  $\hat{b}$  reduced and the solver used to generate additional solutions in  $\hat{Z}^{\hat{p}}_{S,S'}$  for  $\hat{p}$  a  $\hat{b}$ -bit prefix of  $\check{p}$ .

In Sec. 6, we set the error  $\epsilon = 0.4$  and confidence  $\delta = 0.9$  in this method to estimate the sizes of  $\tilde{X}^{\delta}_{S,S'}$  and  $\tilde{X}^{\delta}_{S,S'}$ , from which  $\hat{J}^{\delta}(S,S')$  is estimated using (8). For each set size *n*, we compute  $\hat{J}^{\delta}_{n}$  using  $\geq 100$  hash functions, i.e., implicit selection of pairs *S*, *S'* of expected size *n*.

# 5.3 Sampling $\hat{NS}$ and $\hat{IS}$ for interpretable learning

Similar to the counting process, to construct  $\hat{NS}$  and  $\hat{IS}$ , the sampler will select hash functions H randomly from a family and output values p randomly from its range to solve for tuples  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle$  for which  $H(\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle) = p$  (and are in *NS* or *IS*, respectively). In the following experiments, we will generate up to 100,000 solutions for each of  $\hat{NS}$  and  $\hat{IS}$ , where 70% used for training and 30% used for validation.

We cannot directly encode set difference, used in (9) and (10), using an equivalent quantifier-free formula. To implement a sampler to generate solutions in the set difference, we will use one solver ("E-Solver") to search for candidate solutions and another ("F-Solver") cancel candidates; this is a commonly used algorithm for an SMT solver to solve exist-forall problems (e.g., see Dutertre [2015]).

Here, we will illustrate sampling *IS*, while sampling *NS* is similar. The sampler first uses the E-Solver to generate feasible solutions  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle$  (see (16)) that guarantee, for an attacker's chosen  $\vec{c}$ , the observable value  $\vec{o}$  derived from  $\vec{s}$  with  $\vec{i}$  could be different from an observable  $\vec{o}'$  generated by  $\vec{s}'$  with some  $\vec{i}'$  when the declassified value  $\vec{\Delta}$  is the same. However, it does not guarantee the  $\vec{o}$  is never feasible for  $\vec{s}$ . To further test whether the  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle$  is in  $\hat{IS}$ , we use the F-Solver to test whether  $\langle \vec{s}', \vec{1}'' \rangle$  for some  $\vec{1}''$  could generate  $\vec{o}$  with  $\langle \vec{s}, \vec{i} \rangle$  when they share the declassification value  $\vec{\Delta}$ , to check whether we need to cancel the solution. That is,  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle$  satisfying (16) but not (17) will be included in  $\hat{IS}$ .

After generating enough  $\langle \vec{c}, \vec{i}, \vec{s}, \vec{s}' \rangle$  tuples in  $\hat{NS}$  and  $\hat{IS}$ , the interpretation module trains local support vector machine (SVM) classifiers [Fan et al., 2008] around each of 50 anchor points, after ruling out data whose normalized Euclidean distance (i.e., after scaling each attribute to a value between 0 and 1, use Euclidean distance divided by the number of attributes) is more than 0.2 from the anchor. Then a logistic regression model for *NS* and *IS* is learned using a gradient boosted tree implementation *xgboost* [Chen and Guestrin, 2016]. To generate the interpretable models, we implemented the rule learner using SKOPE-RULES.

#### 6 CASE STUDIES

In this section, we illustrate DINOME by describing its application to the BOOM core (https://github. com/riscv-boom/riscv-boom), an open-source RISC-V core that is susceptible to cache-based side channels and SPECTRE attacks. The goal of these case studies is to illustrate our methodology and to show how it can be useful to system analysts. Our method is also applicable to other side channels, not only cache-based ones. Analysts can specify the secret to protect and define their side channels using attacker-controlled and attacker-observable variables but, critically, not the specific attacker algorithm.

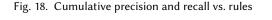

- We applied DINOME to evaluate cache-based side-channel leakage due to secret-dependent memory accesses. With different BOOM configurations (i.e., number of cache ways w and whether to share memory), the case studies shows how  $\hat{J}_n^{\delta}$  curves reveal the effects of the configurations on the leakage. We also implemented and evaluated two possible mitigations, namely SCATTERCACHE [Werner et al., 2019] and PHANTOMCACHE [Tan et al., 2020], which reduce but not eliminate the cache leakage. Our measurements using  $\hat{J}_n^{\delta}$  illustrate which mitigation is better for a specific BOOM setting.

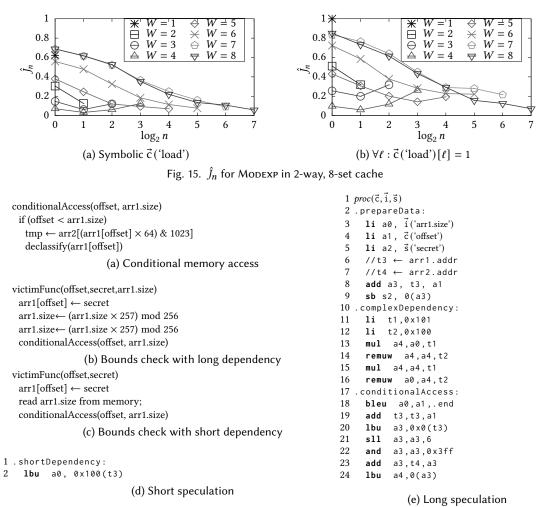

- We used DINOME to assess leakage via cache-based side channels from a modular exponentiation function commonly used in cryptographic algorithms. The rule-based interpretation explains how to choose attacker-controlled variables and which portion of the secret is leaked.

- We evaluated software code snippets causing speculative execution. It demonstrates how to use declassification to focus on leakage caused by speculative execution (i.e., by declassifying other leakage to reveal it) and how to generate efficient interpretable rule set. We found that some software with a short speculation window is insufficient to cause memory leakage in the latest version of BOOM.

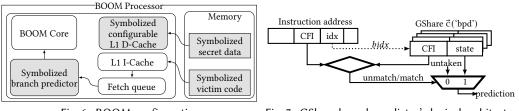

#### 6.1 BOOM configurations

In the following experiments, we used pocket-size hardware modules to replace the modules in the BOOM v2.2.3 configuration. A simplified diagram is shown in Fig. 6. Analyzing artificially small but otherwise faithful configurations of a system is not uncommon in model checking, for example (e.g., Ball et al. [2004], Pnueli et al. [2002]). Specifically, we set the cache line size to *bbytes* = 64B and the total L1 data cache size to 1KB (16 cache lines in total). We then varied the cache ways w and sets c (i.e., subject to  $w \times c = 16$ ) in Sec. 6.2 but used a fixed setting c = 2, c = 8 for other

Fig. 7. GShare branch predictor's logical architecture

evaluations. BOOM only provides a configurable associative L1 cache module using a random replacement policy. To compare different cache designs, we implemented two side-channel-resistant cache modules, as described in Sec. 6.3. For the main memory, we set the memory size to 4KB and thus a memory address is only 12 bits. For evaluation purposes, we used the upper half of the memory address space as instruction memory and the lower half as data memory. To simplify the following analysis, we removed the page table walker module and assumed virtual addresses were the same as physical addresses. For the instruction fetch, we set the fetch width to 4 and configured the L1 instruction cache to a 1KB, 8-set, 2-way cache with a customized prefetching module that preloaded the software workload at the first cycle. One feature of BOOM is that it supports speculative execution, with which we will experiment in Sec. 6.5. Speculative execution leverages a branch predictor, for which we used the GShare branch predictor. The logical structure of GShare is shown in Fig. 7. When a prediction request arrives for a branch instruction, the GShare predictor derives a value *bidx* from the certain bits (denoted 'idx' in Fig. 7) in the instruction address and an instruction history register and then uses *bidx* to index into a table to which we refer as 'bpd'. Each entry of the 'bpd' table includes a label called 'CFI' and a 2-bit 'state', of which one bit indicates whether the entry holds a strong or weak prediction and the other bit holds that prediction (i.e., whether the branch will be taken or not). If the 'bpd{bidx}.CFI' value matches the 'CFI' portion of the instruction address, then the predictor uses the 'bpd{bidx}.state' value to make a branch prediction. The GShare predictor will globally tune entries based on executions in any user's domain. Thus, an attacker can easily affect the 'bpd' table before victim's execution, and so we include 'bpd' in Vars<sub>c</sub>. In our evaluation, we fix the number of 'bpd' entries to 4 so that only 2 bits in the instruction address are used as 'idx' while another 2 bits (=log<sub>2</sub>(fetch width)) are used as its 'CFI' label.

In the following case studies, we added the 'bpd' table in the GShare module to  $Vars_{\vec{c}}$  and registers in the L1 data cache module including the cache metadata, the replacement state (i.e., the linear-feedback shift register (LFSR) for the random replacement policy), and the memory-to-cache mapping (if using a nonfixed mapping) to  $Vars_{\vec{r}}$ .

In cache-based side channel attacks,  $\vec{c}$  and  $\vec{o}$  are not directly represented in the hardware state or in victim's code, and so it is necessary to define them through an adversary model. We assume that the adversary has access to 16 memory blocks  $block_1$ ,  $block_2$ , ...,  $block_\ell$ , ...,  $block_{16}$  aligned to cache lines, which is sufficient to control the cache as our L1 data cache consists of only 16 cache lines in our experiments. Specifically,  $\vec{c}$  ('load')[ $\ell$ ] indicates whether the adversary loads (1) or flushes (0)  $block_\ell$ , while  $\vec{o}$  ('hit')[ $\ell$ ] indicates whether the adversary observes a cache hit (1) or miss (0) when accessing  $block_\ell$ . Appendix 10.2 illustrates how to automatically construct them.

#### 6.2 Cache-based side channels

In this section, we evaluate cache-based side channels under different memory isolation and cache configurations.

| 6.2.1 Without |  |

|---------------|--|

|---------------|--|

shared

memory.

Fig. 8.  $\hat{J}_n$  for PRIME+PROBE attacks

Here, we target a victim's RISC-V assembly *proc* to access a secretindexed memory block not shared with the attacker, by setting the base address in s0 to a value  $0 \times 2000010$ , in contrast to the one used in attacker's process *acc* (see Appendix 10.2). We experimented with different numbers of cache sets *c* including *c* = 1 (i.e., 16-way, 1-set, fully associative), *c* = 2 (i.e., 8-way, 2-set), *c* = 4 (i.e., 4-way, 4-set), *c* = 8 (2-way, 8-set), and *c* = 16 (i.e., 1-way, 16-set, direct-

| proc $(\vec{C}, \vec{I}, \vec{S})$ | )     |                      |

|------------------------------------|-------|----------------------|

| li s0, 0                           | ðx200 | 00010                |

| add s1,                            | s0,   | $\vec{s}$ ('secret') |

| sll s1,                            | s1,   | 6                    |

| lbu a2,                            | 0(s1  | )                    |

|                                    |       |                      |

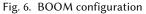

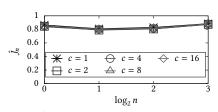

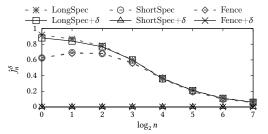

mapped). As shown in Fig. 8(a),  $\hat{J}_n$  increases when the number of sets increases. Specifically, there is no leakage ( $\hat{J}_n = 0$  for all *n*) when c = 1. Using fewer cache sets, each cache set is shared by more memory blocks, and so an attacker will have more difficulty distinguishing one execution from others. When 1 < c < 16,  $\hat{J}_n$  decreases as *n* grows, since the attacker can learn only  $log_2(c)$  bits about the secret and thus may be unable to distinguish secrets in large sets (i.e., large *n*).

An example *interference* rule for *IS* generated as described in Sec. 4 with the highest precision (1.00) and a recall  $\approx$  0.04 in a 2-way, 8-set cache is:

$$\vec{s}(\text{`secret'})[2] \ge 1 \quad \land \quad \vec{s}(\text{`secret'})[1] < 1 \\ \land \quad \vec{s}(\text{`secret'})[0] \ge 1 \quad \land \quad \vec{s}'(\text{`secret'})[1] \ge 1 \\ \end{pmatrix} \land \begin{cases} \vec{c}(\text{`load'})[5] \ge 1 \\ \land \quad \vec{c}(\text{`load'})[13] \ge 1 \end{cases}$$

(18)

In this rule, the  $\vec{s}$  and  $\vec{s}'$  conjuncts concretize the least significant 3 bits of  $\vec{s}$  ('secret') (i.e.,  $\vec{s}$  ('secret')  $\equiv 5 \mod 8$ ) and the lowest bit of  $\vec{s}'$  ('secret') (i.e.,  $\vec{s}'$  ('secret')  $\equiv 0 \mod 2$ ). The  $\vec{c}$  conjuncts are  $\vec{c}$  ('load')[5]  $\geq 1$  and  $\vec{c}$  ('load')[13]  $\geq 1$ ; note that  $13 \equiv 5 \mod 8$ . That is, an attacker could load all blocks *block*<sub>l</sub> with  $l \equiv 5 \mod 8$  into cache to distinguish a secret  $\vec{s}$  ('secret')  $\equiv 5 \mod 8$  from  $\vec{s}'$  ('secret') mod  $8 \in \{0, 2, 4, 6\}$ .

Our approach could not directly represent  $\vec{c}$  ('load')  $[\ell] \equiv \vec{s}$  ('secret') mod *c*. So, the trees in the model split the dataset based on the cache set index. As such, there were many other top-ranking rules similar to (18), each focusing on one residue class of the secret value modulo *c* where c = 8 and constraining  $\vec{c}$  ('load')  $[\ell] = 1$  for all  $\ell$  with that residue class modulo *c*. Each such rule works for  $\frac{1}{8}$  of  $\vec{s}$ 's domain and  $\frac{1}{2}$  of  $\vec{s}$ 's domain, thus only for  $\frac{1}{8} \times \frac{1}{2} \approx 0.06$  of secret pairs. The recall rate 0.04 < 0.06 indicates that priming the corresponding cache set ensures (i.e., precision = 1.0) the interference but is not necessary to cause it.

Analogously, we can generate rules for the *noninterference* set *NS*, as well. One example with precision 1.0 (i.e., that ensures noninterference) and recall 0.11 constrains the secret's least-significant 3 bits to be the same for  $\vec{s}$  and  $\vec{s}'$ :

$$|\vec{s}(\text{'secret'})[2] - \vec{s}'(\text{'secret'})[2]| < 1$$

$$\land |\vec{s}(\text{'secret'})[1] - \vec{s}'(\text{'secret'})[1]| < 1$$

$$\land |\vec{s}(\text{'secret'})[0] - \vec{s}'(\text{'secret'})[0]| < 1$$

(19)

This analysis illustrates that an attacker can easily distinguish  $\vec{s}$  ('secret') and  $\vec{s}'$  ('secret') when priming a cache set used by  $\vec{s}$  ('secret') or  $\vec{s}'$  ('secret') but not both. It is therefore safe to assume that the attacker will PRIME the cache using all its controlled memory blocks to maximize the chances for leakage. The  $\hat{I}_n$  measure under this specific attack is shown in Fig. 8(b). The worst case will leak all of the 4-bit secret when using high-granularity memory-to-cache mapping, i.e., where c = 16.

6.2.2 With shared memory. To evaluate the leakage due to shared memory (i.e., with FLUSH+RELOAD attacks), we allow the attacker to control and observe all memory blocks used by the victim by setting the base to 0x2000000 in *proc* instead of to 0x2000010. The  $\hat{J}_n$  curves are similar and close to 1 for all settings, indicating that the leakage does not have much correlation with w. An example rule for interference derived using the methodology of Sec. 4, having a precision of 1.0 and recall of  $\approx$  0.04, is

Fig. 9.  $\hat{J}_n$  for FLUSH+RELOAD attacks with symbolic  $\vec{c}$  ('load')

$$\vec{s}'(\text{`secret'}) < 2 \land \vec{s}'(\text{`secret'}) \ge 1 \land \vec{c}(\text{`load'})[1] < 1$$

(20)

That is, if  $\vec{s}'(\text{'secret'}) = 1$  then  $\vec{c}(\text{'load'})[1] = 0$  results in interference. Indeed, the other top-ranked rules for this example (not shown) were roughly 32 similar rules, each one setting  $\vec{c}$  ('load')[ $\ell$ ]=0 for a specific secret value  $\vec{s}$  ('secret') =  $\ell$  or  $\vec{s}'$  ('secret') =  $\ell$ . The intuition behind these rules is that an attacker can precisely detect if  $\vec{s}(\text{'secret'}) = \ell$  by setting  $\vec{c}(\text{'load'})[\ell] = 0$  (i.e., FLUSHing *block* so he can later RELOAD it), and similarly for  $\vec{s}'$  ('secret'). Going further, if an attacker sets  $\vec{c}$  ('load')  $[\ell] = 0$  for all  $\ell$ , he can detect the victim's access to any  $block_{\ell}$ , where  $\hat{J}_n = 1$  for all n.

#### Side-channel-resistant cache designs 6.3

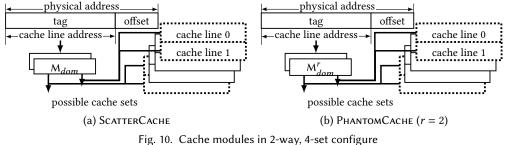

To demonstrate the power of DINOME in comparing different implementations, we evaluate two cache designs for mitigating side channels, namely SCATTERCACHE [Werner et al., 2019] and PHANTOMCACHE [Tan et al., 2020]. Unfortunately, Verilog specifications of these are unavailable, and so we implemented two simplified cache modules (which we continue to refer to as SCATTERCACHE and PHANTOMCACHE) in BOOM following their paper designs.

SCATTERCACHE maps a memory block to a cache line using a cryptographic index derivation function computed using the block's physical address and a private key. As shown in Fig. 10(a), to simulate this index derivation without choosing a concrete function, we use a symbolic look-up table denoted by  $M_{dom}$  per security domain dom (dom = 0 denotes the victim's domain and dom = 1 denotes the attacker's) to store the mapping from memory address to cache line. For security domain dom, its access to memory contents at physical address paddr and so with block address baddr =  $\lfloor paddr/bbytes \rfloor$  is mapped to cache lines with way index k and set index  $j = M_{dom} \{ baddr \} \{ k \}$  for

Fig. 11. Memory sharing enabled with  $\forall \ell : \vec{c} (\text{`load'})[\ell] = 0$  (FLUSH+RELOAD attack)

k = 0, 1, ..., w - 1. Similarly, for PHANTOMCACHE, we used a domain-specific memory-to-cache mapping (shown in Fig. 10(b)) represented by  $M_{dom}^r$  to allow a memory block to use cache lines in *up to r* cache sets indexed by  $M_{dom}^r \{baddr\}\{k\}$  for k = 0, 1, ..., r.<sup>5</sup> In the following evaluation, we have  $M_{dom}, M_{dom}^r \in Vars_{\overline{i}}$ .

6.3.1 Random memory-to-cache mappings. First, we experimented without memory sharing when assuming the memory-to-cache mapping is completely unknown to the attacker. We ended up with  $\hat{J}_n = 0$  for all *n* in both SCATTERCACHE and PHANTOMCACHE. The attacker cannot tell which memory blocks are accessed by the victim, as a memory block could be mapped to any cache line if the mapping is unknown. Thus, we focused on the leakage analysis when memory sharing is enabled.

Intuitively, FLUSH+RELOAD is the best attacker strategy for a normal cache design when memory sharing is enabled. However, for a new cache design, it may not be clear that it is still the best. Our leakage rules provide some insight for SCATTERCACHE and PHANTOMCACHE. For example, one top-ranking rule for SCATTERCACHE, with precision  $\geq 0.80$  and recall of  $\approx 0.02$ , is:

```

\vec{s}(\text{`secret'})[3] \ge 1 \quad \land \quad \vec{s}(\text{`secret'})[2] < 1 \quad \land \quad \vec{s}(\text{`secret'})[1] < 1 \quad \land \quad \vec{s}(\text{`secret'})[0] < 1 \\ \land \quad \vec{1}(\mathsf{M}_0\{8\}\{1\}) \ge 5 \quad \land \quad \vec{1}(\mathsf{M}_1\{8\}\{1\}) \ge 5 \quad \land \quad \vec{c}(\text{`load'})[8] < 1

(21)

```

This rule is similar to (20) but with some additional predicates about  $M_0$ . Specifically, (21) adds  $\vec{i}(M_0\{8\}\{1\}) \ge 5 \land \vec{i}(M_1\{8\}\{1\}) \ge 5$  to the rule when setting  $\vec{c}(\text{`load'})[8] = 0$  (i.e., attacker FLUSHes  $block_8$ ) and  $\vec{s}(\text{`secret'}) = 8$ , which indicates that the  $block_8$  should occupy line k = 1 in set j = 5 in both the victim's and attacker's domains to ensure leakage about whether  $\vec{s}(\text{`secret'}) = 8$  when the attacker RELOADS  $block_8$ .

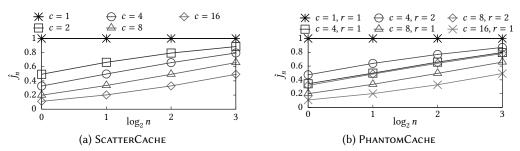

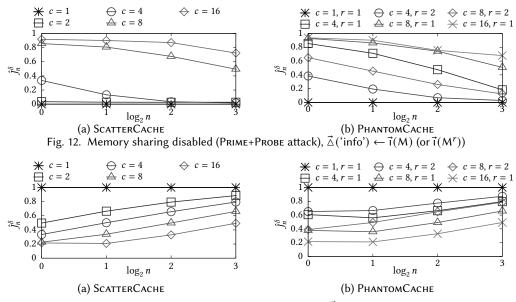

Thus, an attacker should FLUSH+RELOAD all blocks that could share cache lines between victim's and attacker's domain to cause more leakage. Since the memory-to-cache mapping is unknown, an attacker may FLUSH+RELOAD all shared memory blocks. The resulting  $\hat{J}_n$  is shown in Fig. 11(a) for SCATTERCACHE and Fig. 11(b) for PHANTOMCACHE.  $\hat{J}_n$  is high when *n* is large, indicating the attacker can precisely determine  $\vec{s}$  ('secret') when leakage occurs. Our results indicate that lower cache set granularity leaks more: In Fig. 11(a), c = 1 leaks the most, which is similar to the normal cache. When c > 1, the leakage is reduced.

Overall, with same cache set granularity,  $\hat{J}_n$  is higher with PHANTOMCACHE with r = 2 than PHANTOMCACHE with r = 1 and SCATTERCACHE. This is because setting r = 2 allows one physical address to be mapped to more cache sets and so gains more chance to share cache lines across domains.

We also see that  $\hat{J}_n$  for 'c = 8, r = 2' is close to that for 'c = 4, r = 1', as randomly mapping to 2 out of 8 sets is similar to mapping to 1 out of 4 cache sets. Our evaluation results suggests

<sup>&</sup>lt;sup>5</sup>In contrast to the original paper [Tan et al., 2020], we do not force each memory block to map to *r* unique cache sets, i.e., we do not constrain  $M_{dom}^r \{baddr\}\{k\} \neq M_{dom}^r \{baddr\}\{k'\}$  for  $k \neq k'$ .

Fig. 13. Memory sharing enabled (FLUSH+RELOAD attack),  $\vec{\Delta}$  ('info')  $\leftarrow \vec{i}(M)$  (or  $\vec{i}(M^r)$ )

that SCATTERCACHE and PHANTOMCACHE eliminate side-channel leakage when there is no shared memory and largely restrict it when there is shared memory, if the address-to-cache mapping is random and remains unknown to the attacker.

6.3.2 Declassifying the memory-to-cache mapping. When  $\vec{1}(M)$  is unknown to the attacker, our previous analysis shows that cache-based side channels are mitigated. Werner et al. [2019] also discussed the possibility of this mapping being disclosed to the attacker, however, through a profiling procedure. If we declassify  $\vec{1}(M)$ , the interference  $\hat{j}_n^{\delta}$  will increase: Fig. 12(a) shows  $\hat{j}_n^{\delta}$  due to PRIME+PROBE attacks in this case, and Fig. 13(a) shows the impact of this declassification on FLUSH+RELOAD attacks.